EP2SGX30DF780C3

| Part Description |

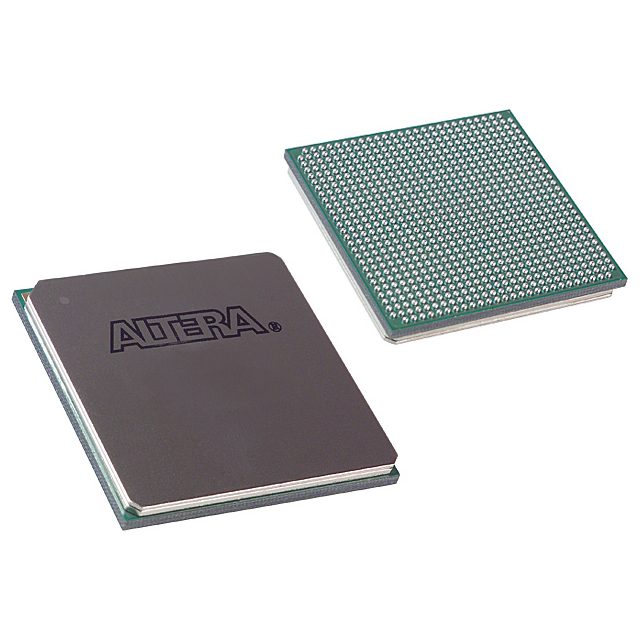

Stratix® II GX Field Programmable Gate Array (FPGA) IC 361 1369728 33880 780-BBGA |

|---|---|

| Quantity | 1,644 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 780-FBGA (29x29) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 780-BBGA | Number of I/O | 361 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 1694 | Number of Logic Elements/Cells | 33880 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 1369728 |

Overview of EP2SGX30DF780C3 – Stratix® II GX FPGA (780-BBGA)

The EP2SGX30DF780C3 is a Stratix® II GX field programmable gate array (FPGA) in a 780-BBGA package designed for high-performance, high-density digital designs. Built on the Stratix II GX family architecture, the device pairs a scalable logic array with high-speed serial transceivers and flexible I/O to address communications, backplane, and protocol-bridging applications.

This device provides a balance of logic capacity, embedded memory, and I/O density for commercial-grade designs that require deterministic supply and temperature operating ranges and RoHS compliance.

Key Features

- Logic Capacity — 33,880 logic elements to implement complex digital functions and control logic efficiently.

- Embedded Memory — Approximately 1.37 Mbits of on-chip RAM for FIFOs, buffers, and local storage.

- I/O and Package — 361 I/O pins in a surface-mount 780-BBGA package (supplier package: 780-FBGA, 29×29) to support dense board-level connectivity.

- Power and Temperature — Core voltage supply range 1.15 V to 1.25 V; commercial operating temperature 0 °C to 85 °C.

- High‑Speed Serial Capability (series feature) — Stratix II GX family transceivers support full‑duplex operation up to 6.375 Gbps per channel for high-bandwidth serial links.

- TriMatrix Memory Architecture (series feature) — Three RAM block sizes enable dual-port memory and high-performance FIFO implementations.

- DSP and Clocking (series feature) — Integrated high-speed DSP blocks and up to four enhanced PLLs provide dedicated multiplier/accumulate resources and flexible clock management.

- Protocol and Memory Support (series feature) — Series-level support for external memory interfaces (QDR, DDR, DDR2, SDR) and common serial protocols for system-level integration.

- Signal Integrity Features (series feature) — Transceiver options include programmable VOD, pre-emphasis, adaptive equalization, and selectable on‑chip termination resistors for robust link performance.

- Compliance — RoHS compliant for environmental and manufacturing compatibility.

Typical Applications

- High-Speed Communications — Implement multi‑Gbps serial links and protocol bridging where series transceiver features and SERDES capability are required.

- Backplane and Networking Equipment — Use the device’s dense I/O and transceiver performance for backplane interfaces and packet/transport processing.

- Memory Interface and Buffering — Leverage embedded RAM and TriMatrix memory organization for high‑performance FIFOs and external memory controllers.

- Signal Processing and DSP Tasks — Employ integrated DSP blocks for multiply-accumulate and FIR filter implementations in communications and processing pipelines.

Unique Advantages

- Balanced Logic and Memory — 33,880 logic elements combined with ~1.37 Mbits of embedded memory supports complex, on‑chip buffering and control tasks.

- High I/O Density in a Compact Package — 361 I/Os in a 780-BBGA (29×29) footprint enables dense board integration without sacrificing connectivity.

- Series-Level High-Speed Serial Support — Stratix II GX transceivers provide up to 6.375 Gbps per channel and signal‑integrity features to simplify high‑bandwidth link design.

- Flexible Clocking and DSP Resources — Enhanced PLLs and dedicated DSP blocks allow precise timing control and efficient implementation of arithmetic-intensive functions.

- Commercial-Grade Reliability — Specified operating range of 0 °C to 85 °C and controlled supply voltage ensure predictable behavior in commercial applications.

- Regulatory Compatibility — RoHS compliance supports environmentally conscious manufacturing processes.

Why Choose EP2SGX30DF780C3?

The EP2SGX30DF780C3 delivers a practical combination of logic density, embedded memory, and I/O connectivity in a commercial-grade Stratix II GX FPGA package. Its architecture—backed by family-level transceiver, memory, and DSP features—makes it suitable for designs requiring high-bandwidth serial links, substantial on-chip buffering, and flexible clocking resources.

This device is well suited to system designers who need scalable performance with verified series-level capabilities and straightforward integration into surface-mount, high-density board layouts. Its RoHS compliance and defined operating specifications make it a dependable choice for commercial electronic products and communications equipment.

Request a quote or submit a pricing and availability request to evaluate EP2SGX30DF780C3 for your next design project.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018